Innovation for the next generation

Clock Synthesizer for Jitter Tolerance Testing | Sinusoidal Jitter Generation | Multi-UI Clock Frequency Modulation

20 MHz to 5.5 GHz Operation | Two Differential Clock Outputs | Low Intrinsic Jitter | FM and PM Modulation |

# Summary

With the accelerated growth of hyperscale datacenters, the performance demands on Ethernet network infrastructure is increasing exponentially, and customer expectations for high-speed data throughput is at an all-time high. As a result, Bit Error Rate Testers (BERT) have become a cornerstone for physical layer testing, from qualifying bit transmission for fiber optic and copper-wire digital data transmission lines to testing signal integrity.

A BERT generates a sequence of bits through a communication channel and the received bits are then compared against the transmitted bits. A Bit Error Ratio (BER) evaluates the full end-to-end performance of a connectivity system and assures communication reliability.

The ML407-PAM is an add-on instrument for the MultiLane BERTs, intended for jitter tolerance (JTOL) receiver stress testing. It enables injection of multi-UI sinusoidal jitter, BUJ and random jitter to a clean NRZ or PAM4 signal coming out of the BERT. The ML407-PAM is intended for users seeking to do stressed input testing on their receivers in accordance with OIF-CEI VSR56 PAM or IEEE 802.3 CAUI-4.

# **ML407-PAM**

# 5.5 GHz Clock Synthesizer

## Introduction

The ML407-PAM is an add-on instrument for the ML BERT that can be configured as a clock synthesizer with frequencies ranging from 0.02 to 5.5 GHz

#### **Key Features**

- 0.02 to 5.5 GHz operation

- Two differential clock outputs

- Low intrinsic jitter

- FM and PM Modulation

- -110 dBc/Hz at 100 kHz

#### **Target Applications**

ML BERT's clock source for jitter tolerance testing and general serial data receiver characterization.

#### **Clock Source**

ML407-PAM clock synthesizer generates two pairs of differential clock outputs from 20 MHz to 5.5 GHz.

#### **Setup**

ML407 clock out is connected to the clock IN of BERT (ML4039D in this example), while the other clock output on the ML407 is terminated with 50  $\Omega$ .

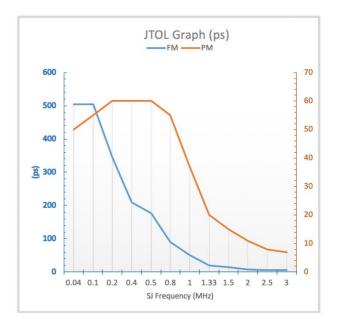

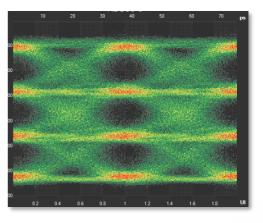

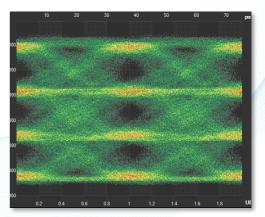

**JTOL Graph**

These values were obtained using ML4039D BERT + PX1015D DSO + ML407-PAM Clock Source. The signal is 26.5625 GBd PAM4, and the patterns used are PRBS7 and square wave.

When using the ML407-PAM along with MultiLane BERT instruments, the TX CMU PLL of the driving chip tracks out jitter from its incoming reference CLK at 4 MHz and beyond\*, which explains the behavior seen in the JTOL graph. Jitter observed from 4 to 40 MHz is typically out of band noise or crosstalk.

\*JTOL SJ jitter impairment from 4 to 40 MHz is not strictly compliant with the stressed receiver sensitivity specification described in the IEEE 802.3bs document, Annex 120D.

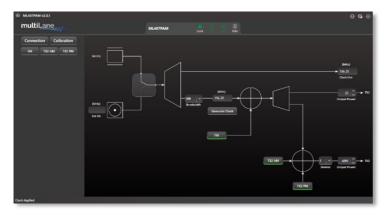

# **Graphical User Interface**

The GUI is divided into 6 sections as follows:

#### Connection

The ML407-PAM has a static IP address and an Ethernet interface that connects to your Windows OS. The very first thing to do in the GUI is to establish a TCP/IP connection to the device.

#### Calibration

The ML407-PAM can be used with no calibration, Factory Calibration (done by ML), or Custom calibration created by the customer using the "Calibration Wizard" that allows the user to save jitter values for each slider position.

#### **Clock Configuration**

The ML407-PAM has a built-in reference oscillator that is active when the switch is turned downwards.

| Range of bit rates | Divider | Example                                   |

|--------------------|---------|-------------------------------------------|

| 25 Gbps or GBd     | 170     | For 26.5625 Gbps, use<br>156.25 MHz clock |

| 50 Gbps or GBd     | 340     | For 53.125 Gbps, use<br>156.25 MHz clock  |

#### FM

FM modulation is the basis for injecting sinusoidal jitter SJ on a PRBS pattern coming out of the BERT. Use the FM controls to do JTOL tests per IEEE or OIF-CEI.

#### PM

PM stands for phase modulation and is only available on TX2 of the ML407-PAM. PM modulates the phase of the clock coming out of the ML407-PAM, either in a sinusoidal way, a random way or as BUJ.

#### AM

AM stands for amplitude modulation and is only available on TX2 of the ML407-PAM. AM modulation is the basis for injecting random vertical noise on a PRBS pattern coming out of the BERT.

### **Specifications**

#### Synthesizer

| Parameter                       | Specifications                                     |

|---------------------------------|----------------------------------------------------|

| Frequency Range                 | 20 MHz to 5.5 GHZ                                  |

| Frequency Resolution            | 1 Hz                                               |

| TX1 Amplitude Range             | 1.8 Vpp max, differential                          |

| TX2 Amplitude Range             | 1.8 Vpp max, differential                          |

| TX2 Clock Divider               | 1/2/4/8                                            |

| External Clock                  | Single ended or differential input (5 to 1400 MHz) |

| External Clock Input<br>voltage | 0.2 – 2 Vpp, differential                          |

#### **Electrical**

| Parameter                  | Specifications    |

|----------------------------|-------------------|

| Power Requirements         | 12 V 1 A          |

| Mechanical                 |                   |

| Parameter                  | Specifications    |

| TX/RX Connectors           | SMA               |

| Box Dimensions (W x L x H) | 154 x 161 x 32 mm |

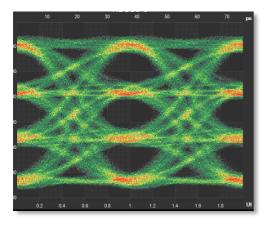

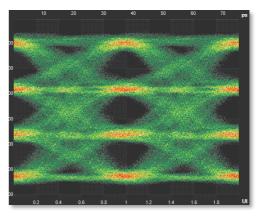

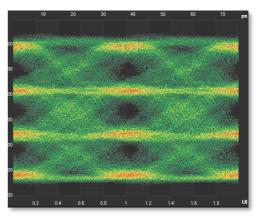

## **Appendix A: Jitter Modulation Examples**

These examples use the ML407-PAM clock synthesizer to supply a reference clock to the ML4039D 28GBd PAM4 BERT

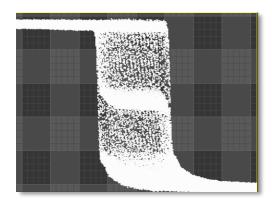

Figure 1: 500 ps SJ Jitter at 40 kHz

Figure 2: 170 ps SJ Jitter at 0.5 MHz

Figure 3: Clean PAM4 eye diagram at 26.5625 GBd

Figure 4: With SJ Jitter at 100 kHz

Figure 5: With SJ Jitter at 1 MHz

Figure 6: With FM-RJ at 3000 steps

Figure 7: With PM at 0.5 MHz

# **Ordering Information**

| Option    | Description                    | 32mm        |  |

|-----------|--------------------------------|-------------|--|

| ML407-PAM | JTOL Clock Synthesizer 5.5 GHz |             |  |

|           |                                | 154mm 161mm |  |

#### **Recommended Accessories**

| Instruments | Recommended cables      | Comments                                       |

|-------------|-------------------------|------------------------------------------------|

| ML407-PAM   | 1x MLCBPM-2.92-30/60/80 | 2.92 mm connector 2x1 channel, 30, 60 or 80 cm |

| ML407-PAM   | 1x MLCBPM-SMA-30/60/80  | 3.5 mm connector 2x1 channel, 30, 60 or 80 cm  |

Please contact us at sales@multilaneinc.com.

**North America** 48521 Warm Springs Blvd. Suite 310 Fremont, CA 94539 USA +1 510 573 6388 Worldwide

Houmal Technology Park Askarieh Main Road Houmal, Lebanon +961 81 794 455 Asia

14F-5/ Rm.5, 14F., No 295 Sec.2, Guangfu Rd. East Dist., Hsinchu City 300, Taiwan (R.O.C) +886 3 5744 591